# ASYMMETRICAL-BIDIRECTIONAL THYRISTOR OVERVOLTAGE PROTECTOR

## TISP4A250H3BJ Overvoltage Protector

#### **RING Line Protection for:**

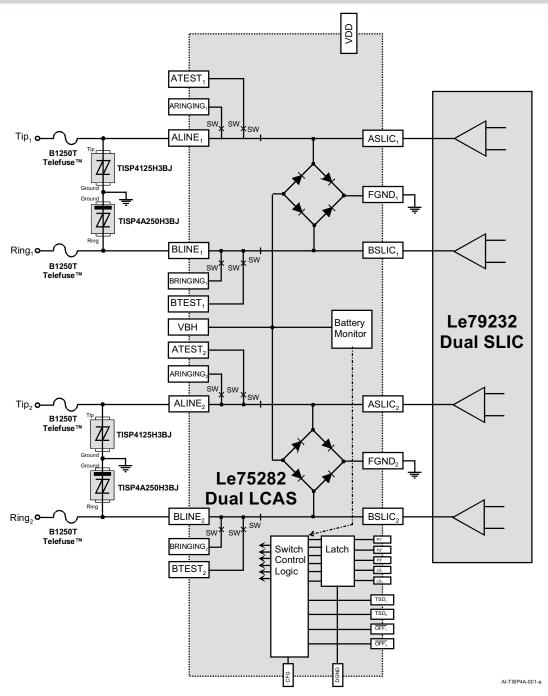

LCAS (Line Card Access Switch) such as Le75181, Le75183 and Le75282

#### **Voltages Optimized for:**

- Battery-Backed Ringing Circuits

Maximum Ringing a.c.....104 Vrms

Maximum Battery Voltage .......52 V

| Device Name     | V <sub>DRM</sub><br>V | V <sub>(BO)</sub><br>V |

|-----------------|-----------------------|------------------------|

| TISP4A250H3BJ   | +100                  | +125                   |

| 1101 4/25011000 | -200                  | -250                   |

### **Rated for International Surge Wave Shapes**

| Wave Shape | Standard         | I <sub>PPSM</sub><br>A |

|------------|------------------|------------------------|

| 2/10       | GR-1089-CORE     | 500                    |

| 8/20       | IEC 61000-4-5    | 300                    |

| 10/160     | TIA-968-A        | 250                    |

| 10/700     | ITU-T K.20/21/45 | 200                    |

| 10/560     | TIA-968-A        | 160                    |

| 10/1000    | GR-1089-CORE     | 100                    |

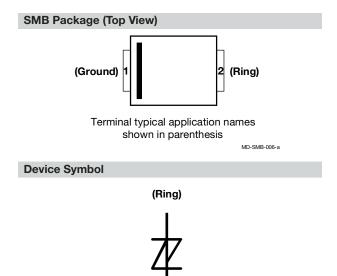

(Ground)

**71**%

.....UL Recognized Component

#### **How To Order**

| Device        | Package Carrier Order As |                      | , , , , , , , , , , , , , , , , , , , |        |      |

|---------------|--------------------------|----------------------|---------------------------------------|--------|------|

| TISP4A250H3BJ | SMB                      | Embossed Tape Reeled | TISP4A250H3BJR-S                      | 4A250H | 3000 |

#### **Description**

The TISP4A250H3BJ is an asymmetrical bidirectional overvoltage protector. It is designed to limit the peak voltages on the Ring line terminal of the LCAS (Line Card Access Switch) such as Le75181, Le75183 and Le75282. The TISP4A250H3BJ must be connected with bar-indexed terminal 1 to the protective Ground, and terminal 2 to the Ring conductor.

The TISP4A250H3BJ voltages are chosen to give adequate LCAS ring line terminal protection for all switch conditions. The most potentially stressful condition is low level power cross when the LCAS switches are closed. Under this condition, the TISP4A250H3BJ limits the voltage and corresponding LCAS dissipation until the LCAS thermal trip operates and opens the switches.

Under open-circuit ringing conditions, the line Ring conductor will have high peak voltages. For battery backed ringing, the Ring conductor will have a larger peak negative voltage than positive, i.e. the peak voltages are asymmetric. The TISP4A250H3BJ has a similar voltage asymmetry and will allow the maximum possible ringing voltage, while giving the most effective protection. On a connected line, the Tip conductor will have much smaller voltage levels than the open-circuit Ring conductor values. Here a TISP4xxxH3BJ series symmetrical voltage protector gives adequate protection.

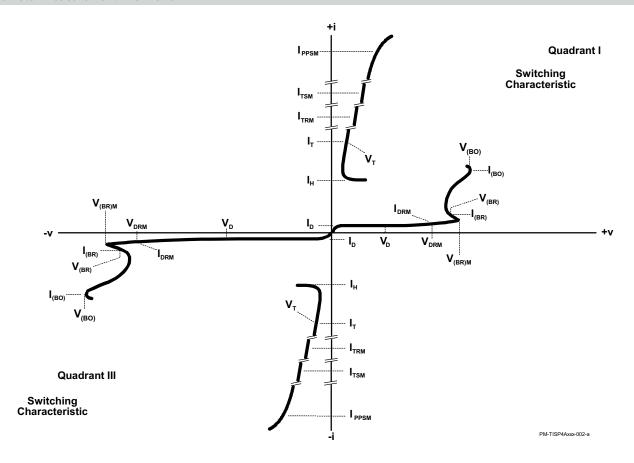

Overvoltages are initially clipped by breakdown clamping. If sufficient current is available from the overvoltage, the breakdown voltage will rise to the breakover level, which causes the device to switch into a low-voltage on-state condition. This switching action removes the high voltage stress from the following circuitry and causes the current resulting from the overvoltage to be safely diverted through the protector. The high holding (switch off) current helps prevent d.c. latchup as the diverted current subsides.

## TISP4A250H3BJ Overvoltage Protector

## **BOURNS**®

#### Absolute Maximum Ratings, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

| Rating                                                                                                                                                                                                                                                                                                                                                                                                                              | Symbol              | Value                                                | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------|------|

| Repetitive peak off-state voltage (see Note 1)                                                                                                                                                                                                                                                                                                                                                                                      |                     | +100<br>-200                                         | V    |

| Non-repetitive peak impulse current (see Notes 2 and 3)                                                                                                                                                                                                                                                                                                                                                                             |                     |                                                      |      |

| 2/10 μs (GR-1089-CORE, 2/10 μs voltage wave shape) 8/20 μs (IEC 61000-4-5, 1.2/50 μs voltage, 8/20 μs current combination wave generator) 10/160 μs (TIA-968-A, 10/160 μs voltage wave shape) 5/310 μs (ITU-T K.44, 10/700 μs voltage wave shape used in K.20/21/45) 5/320 μs (TIA-968-A, 9/720 μs voltage wave shape) 10/560 μs (TIA-968-A, 10/560 μs voltage wave shape) 10/1000 μs (GR-1089-CORE, 10/1000 μs voltage wave shape) | I <sub>PPSM</sub>   | ±500<br>±300<br>±250<br>±200<br>±200<br>±160<br>±100 | A    |

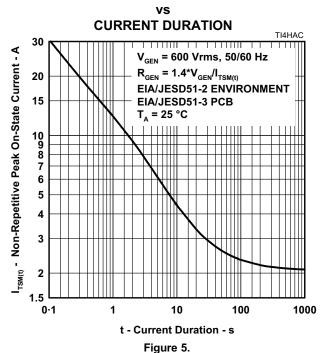

| Non-repetitive peak on-state current (see Notes 2, 3 and 4) 20 ms, 50 Hz (full sine wave) 16.7 ms, 60 Hz (full sine wave) 1000 s, 50 Hz or 60 Hz a.c.                                                                                                                                                                                                                                                                               | I <sub>TSM</sub>    | 55<br>60<br>2.2                                      | А    |

| Initial rate of rise of on-state currrent, exponential current ramp. Maximum ramp value < 200 A                                                                                                                                                                                                                                                                                                                                     | di <sub>T</sub> /dt | 400                                                  | A/μs |

| Junction temperature                                                                                                                                                                                                                                                                                                                                                                                                                | TJ                  | -40 to +150                                          | °C   |

| Storage temperature range                                                                                                                                                                                                                                                                                                                                                                                                           | T <sub>stg</sub>    | -65 to +150                                          | °C   |

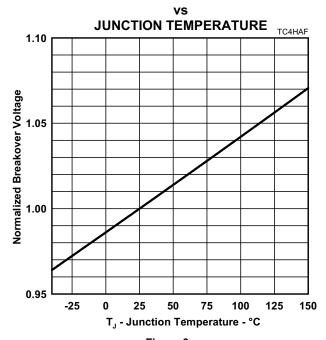

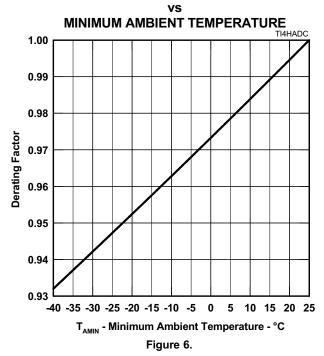

NOTES: 1. See Figure 6 for voltages at other temperatures.

- 2. Initially the device must be in thermal equilibrium with  $T_J = 25$  °C.

- 3. The surge may be repeated after the device returns to its initial conditions.

- 4. EIA/JESD51-2 environment and EIA/JESD51-3 PCB with standard footprint dimensions connected with 5 A rated printed wiring track widths. See Figure 5 for the current ratings at other durations. Derate current values at -0.61 %/°C for ambient temperatures above 25 °C.

#### Overload Ratings, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

| Rating                                                                                   | Symbol  | Value | Unit  |

|------------------------------------------------------------------------------------------|---------|-------|-------|

| Maximum overload on-state current without open circuit, 50 Hz or 60 Hz a.c. (see note 5) |         |       |       |

| 0.03 s                                                                                   |         | 60    |       |

| 0.07 s                                                                                   |         | 40    | A rmo |

| 1.6 s                                                                                    | IT(OV)M | 8     | A rms |

| 5.0 s                                                                                    |         | 7     |       |

| 1000 s                                                                                   |         | 2.2   |       |

NOTE: 5. Peak overload on-state current during a.c. power cross tests of GR-1089-CORE and UL 1950/60950. These electrical stress levels may damage the TISP4A250H3BJ silicon die. After test, the pass criterion is either that the device is functional or, if it is faulty, that it has a short-circuit fault mode. In the short-circuit fault mode, the following equipment is protected as the device is a permanent short across the line. The equipment would be unprotected if an open-circuit fault mode developed.

# TISP4A250H3BJ Overvoltage Protector

## **BOURNS®**

## Electrical Characteristics, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

|                   | Parameter                                  | Test Conditions                                                  |                                                  | Min  | Тур | Max          | Unit  |

|-------------------|--------------------------------------------|------------------------------------------------------------------|--------------------------------------------------|------|-----|--------------|-------|

| I <sub>DRM</sub>  | Repetitive peak off-state current          | V <sub>D</sub> = V <sub>DRM</sub>                                | T <sub>A</sub> = 25 °C<br>T <sub>A</sub> = 85 °C |      |     | ±5<br>±10    | μΑ    |

| V <sub>(BO)</sub> | Breakover voltage                          | $dv/dt = \pm 250 \text{ V/ms}, R_{SOURCE} = 300 \Omega$          |                                                  |      |     | +125<br>-250 | ٧     |

| I <sub>(BO)</sub> | Breakover current                          | $dv/dt = \pm 250 \text{ V/ms}, R_{SOURCE} = 300 \Omega$          |                                                  | ±150 |     | ±600         | mA    |

| V <sub>T</sub>    | On-state voltage                           | I <sub>T</sub> = ±5 A, t <sub>w</sub> = 100 μs                   |                                                  |      |     | ±3           | V     |

| I <sub>H</sub>    | Holding current                            | $I_T = \pm 5 \text{ A, di/dt} = \pm 30 \text{ mA/ms}$            |                                                  | ±150 |     | ±600         | mA    |

| dv/dt             | Critical rate of rise of off-state voltage | Linear voltage ramp<br>Maximum ramp value < 0.85V <sub>DRM</sub> |                                                  | ±5   |     |              | kV/µs |

| Co                | Off-state capacitance                      | f = 1 MHz, V <sub>d</sub> = 1 V rms                              | V <sub>D</sub> = 2 V                             |      |     | 72           | pF    |

## Thermal Characteristics, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

|                                                         | Parameter                                                              | Test Conditions                    | Min | Тур | Max  | Unit |

|---------------------------------------------------------|------------------------------------------------------------------------|------------------------------------|-----|-----|------|------|

| $R_{\theta JA}$ Junction to ambien t thermal resistance | EIA/JESD51-3 PCB, I <sub>T</sub> = I <sub>TSM(1000)</sub> (see Note 6) |                                    |     |     | 113  | °C/W |

|                                                         | 265 mm x 210 mm populated line card,                                   |                                    | 50  |     | C/VV |      |

|                                                         |                                                                        | 4-layer PCB, $I_T = I_{TSM(1000)}$ |     |     |      |      |

NOTE: 6. EIA/JESD51-2 environment and PCB has standard footprint dimensions connected with 5 A rated printed wiring track widths.

#### **Parameter Measurement Information**

Figure 1. Voltage-Current Characteristic for the Ring and Ground Terminals All Measurements are Referenced to the Ground Terminal

### **Typical Characteristics**

## **OFF-STATE CURRENT** vs **JUNCTION TEMPERATURE** TCHAG 100 $V_{D} = \pm 50 \text{ V}$ 10 |I<sub>p</sub>| - Off-State Current - µA o o o 0.001 -25 50 75 100 125 150 T<sub>J</sub> - Junction Temperature - °C

Figure 2.

### NORMALIZED BREAKOVER VOLTAGE

Figure 3.

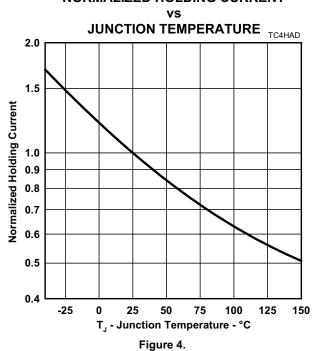

### **NORMALIZED HOLDING CURRENT**

### **Rating and Thermal Information**

## **NON-REPETITIVE PEAK ON-STATE CURRENT**

## **V**<sub>DRM</sub> **DERATING FACTOR**

### **Applications Information**

Figure 7. Typical Application Circuit

#### **Bourns Sales Offices**

| Region        | Phone           | Fax             |

|---------------|-----------------|-----------------|

| The Americas: | +1-951-781-5500 | +1-951-781-5700 |

| Europe:       | +41-41-7685555  | +41-41-7685510  |

| Asia-Pacific: | +886-2-25624117 | +886-2-25624116 |

#### **Technical Assistance**

| Region        | Phone           | Fax             |

|---------------|-----------------|-----------------|

| The Americas: | +1-951-781-5500 | +1-951-781-5700 |

| Europe:       | +41-41-7685555  | +41-41-7685510  |

| Asia-Pacific: | +886-2-25624117 | +886-2-25624116 |

## www.bourns.com

Bourns® products are available through an extensive network of manufacturer's representatives, agents and distributors. To obtain technical applications assistance, a quotation, or to place an order, contact a Bourns representative in your area.

Reliable Electronic Solutions