Notizie

DAC esplora il ruolo di AI e ML in tutti i mercati

Il Moscone Center di San Francisco ospiterà il DAC dal 25 al 28 giugno

Soluzioni OneSpin e Austemper Design Systems entrambi evidenzieranno gli strumenti per la verifica della sicurezza funzionale. Austemper si concentrerà sullo sviluppo di sistemi mission-critical, con la suite di strumenti KaleidoScope che supporta la progettazione analogica per la propagazione di guasti simultanei a segnali misti. La suite di strumenti automatizzati offre funzionalità di analisi, sintesi e verifica della sicurezza per applicazioni orientate alla certificazione. Viene utilizzato per progetti automobilistici su larga scala in ADAS e guida autonoma. La simulazione di guasto simultaneo include le simulazioni raccomandate da ISO 26262 per soddisfare i requisiti ASIL.

La società ha recentemente collaborato con OneSpin Solutions per adottare una metodologia supportata da strumenti per le applicazioni di sicurezza funzionale, combinando un flusso di progettazione e verifica, che sarà dimostrata presso lo stand OneSpin. I meccanismi di sicurezza hardware sono inseriti nei progetti di chip e gli strumenti di OneSpin Solutions verificano formalmente la logica di sicurezza dell'hardware. Il controllo di equivalenza garantisce che la logica di sicurezza inserita non influenzi la funzionalità regolare e l'analisi di rilevamento dei guasti verifica che i meccanismi di sicurezza funzionino correttamente in caso di errori casuali.

OneSpin promuove anche il suo kit di qualificazione degli strumenti, in seguito alla verifica da parte di TÜV SÜD dei suoi processi di sviluppo degli utensili. Il kit iniziale è disponibile per lo strumento EDA 360 EC-FPGA dell'azienda, un controllo di equivalenza sequenziale automatico che impedisce ai flussi di progettazione FPGA di introdurre errori di implementazione. Il kit è certificato ISO 26262, IEC 61508 e EN 50128.

Approfondimenti FPGA

Ancora con il design FPGA, Plunify ha collaborato con Xilinx per offrire la suite di design Vivado nel cloud, tramite la piattaforma Plunify Cloud. I progettisti pagano appena 50 c per compilare un progetto Vivado sul cloud di Amazon Web Services (AWS), comprese le licenze.

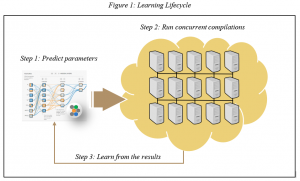

La compagnia dimostrerà anche miglioramenti al suo software di chiusura temporizzazione InTime per ottimizzare i tempi FPGA nel cloud (Figura 1). InTime Optimization Methodology può migliorare la frequenza di clock del 20-80% e soddisfare i requisiti di temporizzazione in giorni, anziché settimane tramite l'apprendimento automatico. Il software accelera anche la chiusura dei tempi e l'ottimizzazione ed è accessibile tramite il cloud.

La compagnia dimostrerà anche miglioramenti al suo software di chiusura temporizzazione InTime per ottimizzare i tempi FPGA nel cloud (Figura 1). InTime Optimization Methodology può migliorare la frequenza di clock del 20-80% e soddisfare i requisiti di temporizzazione in giorni, anziché settimane tramite l'apprendimento automatico. Il software accelera anche la chiusura dei tempi e l'ottimizzazione ed è accessibile tramite il cloud.

Promuovere la tecnologia eFPGA, Achronix Semiconductor sta collaborando con lo specialista IP CAST per aumentare il throughput e fare risparmi nell'archiviazione della memoria.

I due espositori spiegheranno in che modo l'IP di compressione lossless di CAST è stato trasferito al portafoglio FPGA di Achronix per l'uso in applicazioni di trasferimento dati di data center e mobili. L'implementazione hardware dello standard di compressione lossless per Deflate, GZIP e ZLIB, è compatibile con le implementazioni software utilizzate per compressione o decompressione per fornire throughput fino a 100Gbit / s con bassa compressione e bassa latenza, accoppiata alla tecnologia Speedcore eFPGA per spostare e archiviare grandi dati a basso consumo energetico.

CAST ha portato il suo IP agli FPGA di Achronix

Efficienza energetica

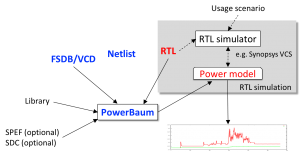

A proposito di power management, un altro espositore, Baumidentifica l'efficienza energetica come l'area meno sviluppata nella progettazione dei chip. Il suo strumento automatizzato di analisi e modellazione della potenza è progettato per progetti automobilistici, IoT, mobili, di rete e server. PowerBaum 2.0 (Figura 3) supporta l'alimentazione dinamica e statica, include le descrizioni RTL e netlist e aggiunge il supporto per l'analisi dell'alimentazione con l'emulazione hardware. Questo, dice l'azienda, consente agli ingegneri di correggere gli errori di alimentazione in scenari software realistici. Lo strumento supporta anche l'analisi con temperature arbitrarie specificate dai progettisti per valutare gli effetti della temperatura sul consumo energetico di un progetto.

Alla DAC, la società introdurrà anche PowerWurzel, un motore di analisi di potenza a livello di porta da integrare con PowerBaum per la modellazione di potenza.

Figura 3 Gli strumenti di Baum analizzano l'efficienza energetica

Strumenti di progettazione e verifica SoC basati su cloud per il design IC Metrica include Cloud Simulator e Verification Manager, progettati per gestire i requisiti e le risorse di simulazione, regolandoli su o giù ogni minuto. La società afferma che Google Cloud consente una capacità di simulazione SystemVerilog illimitata e compatibile con UVM e una gestione di verifica nativa basata su web per tempi di regressione più rapidi, errori di codice di linea ridotti e copertura di codice prevedibile.

Oltre agli espositori, l'evento ospita sessioni tecniche e un programma di keynote che affrontano le aree di attualità. Quest'anno, ad esempio, Cadence ospiterà un'esercitazione su "Sicurezza funzionale e affidabilità per le applicazioni automobilistiche" e una sull'apprendimento automatico ("Machine Learning porta le prestazioni di riconoscimento vocale al livello successivo"). Una nota chiave di Anna-Katrina Shedletsky, Instrumental, lunedì 25 giugno, si concentrerà su "Automating Intelligence: Machine Learning e il futuro della produzione". L'utilizzo di ML e AI per la robotica dell'assistenza sociale (SAR) è esplorato nella nota di giovedì di Maja Matarić, University of Southern California, che presenterà "Automation vs Augmentation: Socialocs Assistive Robotocs e il futuro del lavoro".

Un'altra nota fondamentale sostiene RISC-V come mezzo per liberare gli architetti dalle architetture di set di istruzioni proprietarie (ISA). David A Patterson, Google e University of California, presenteranno 'A New Golden Age per Computer Architecture: Domain Specific Accelerators e Open RISC-V'.

Una nuova area quest'anno al DAC è il Design Infrastructure Alley. L'iniziativa del Alleanza ESD e associazione per professionisti del calcolo ad alte prestazioni è un'area dedicata all'infrastruttura IT per la progettazione di sistemi e componenti elettronici. Oltre ai requisiti di elaborazione e archiviazione per la progettazione e la gestione dell'uso del cloud, è disponibile un padiglione dedicato al Design-on-the-Cloud che discute gestione delle licenze, grid computing e sicurezza dei dati.