Notizie

dsPIC ottiene due core a 16 bit veloci per accelerare lo sviluppo della potenza e del controllo motore ad alte prestazioni

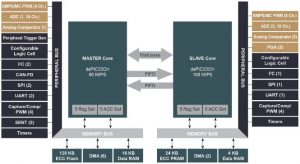

Destinato a velocizzare lo sviluppo del codice rimuovendo la dipendenza tra interfaccia utente e codice in tempo reale, i nuclei sono in gran parte indipendenti, ognuno con il proprio set di periferiche e comunicano tra loro solo tramite FIFO e caselle postali - i bus dati e di indirizzo sono non condiviso.

Entro dsPIC33CH, poiché la famiglia sarà conosciuta, i core sono simili, con uno funzionante a 90MHz designato come "master" e uno "slave" a 100MHz. Il master ha più interfacce seriali, mentre lo slave ha più ADC, canali PWM e comparatori, ad esempio (vedi diagramma).

"Il core slave è utile per l'esecuzione di un codice di controllo dedicato e time-critical mentre il core master è occupato nell'esecuzione dell'interfaccia utente, del monitoraggio del sistema e delle funzioni di comunicazione, personalizzato per l'applicazione finale", ha affermato l'azienda. "Il dsPIC33CH è progettato specificamente per facilitare lo sviluppo di codice indipendente per ogni core da parte di team di progettazione separati e consente un'integrazione perfetta quando sono riuniti in un unico chip.

Le potenziali applicazioni includono l'alimentazione digitale e il controllo del motore, ad esempio in alimentazione wireless, server, droni e sensori automobilistici.

In un alimentatore digitale, secondo Microchip, il core slave gestisce gli algoritmi intensivi matematici, mentre il core master gestisce in modo indipendente lo stack del protocollo PMBus e fornisce il monitoraggio del sistema. In una ventola o una pompa per autoveicoli, il core slave gestirà la velocità e il controllo della coppia critici nel tempo mentre il master gestisce la comunicazione CAN-FD (CAN-flexible data-rate), il monitoraggio del sistema e la diagnostica.

Gli aggiornamenti del firmware live ("zero down-time") sono possibili su entrambi i core, poiché ciascuno di essi ha due negozi di programmi flash: quattro in totale.

Se non sono necessari aggiornamenti dal vivo, il doppio della quantità di memoria del programma è disponibile per il core.

Rispetto alla precedente famiglia dsPIC rivolta allo stesso mercato - dsPIC33EP / GS - le prestazioni sono quasi raddoppiate (latenza da 543ns a 280ns) - parzialmente attraverso la velocità di clock passando da 70MHz a 100MHz e parzialmente attraverso: commutazione di contesto più veloce (accumulatori sensibili al contesto e registri di stato) e nuove istruzioni (divisione più veloce, carico / archivio a 32 bit).

Sono disponibili otto varianti di pacchetto, dal pin dsPIC33CH64MP202 fino a 80 pin e da 5 x 5 mm verso l'alto.

Le opzioni Flash vanno da 64 a 128kbyte.

Il supporto proviene da:

- MPLAB X IDE

- Configuratore di codice

- Scheda Curiosità dsPIC33CH (DM330028)

- Modulo plug-in dsPIC33CH per controllo motore (MA330039) per MCLV-2 e MCHV-2/3

- Modulo plug-in dsPIC33CH per piattaforme generiche (MA330040) per Explorer 16/32 (DM240001-2)